info@atrinelec.com

@atrinelec

# High-Speed, Low-Power Dual Operational Amplifier

## AD826

## FEATURES

**High Speed:** 50 MHz Unity Gain Bandwidth 350 V/µs Slew Rate 70 ns Settling Time to 0.01% Low Power: 7.5 mA Max Power Supply Current Per Amp Easy to Use: **Drives Unlimited Capacitive Loads** 50 mA Min Output Current Per Amplifier Specified for +5 V, ±5 V and ±15 V Operation 2.0 V p-p Output Swing into a 150  $\Omega$  Load  $(V_{S} = +5 V)$ **Good Video Performance** Differential Gain & Phase Error of 0.07% & 0.11° **Excellent DC Performance:** 2.0 mV Max Input Offset Voltage

APPLICATIONS Unity Gain ADC/DAC Buffer Cable Drivers 8- and 10-Bit Data Acquisition Systems Video Line Driver Active Filters

### **PRODUCT DESCRIPTION**

The AD826 is a dual, high speed voltage feedback op amp. It is ideal for use in applications which require unity gain stability and high output drive capability, such as buffering and cable driving. The 50 MHz bandwidth and 350 V/ $\mu$ s slew rate make the AD826 useful in many high speed applications including: video, CATV, copiers, LCDs, image scanners and fax machines.

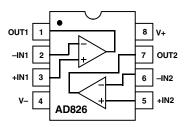

### CONNECTION DIAGRAM 8-Lead Plastic Mini-DIP and SO Package

The AD826 features high output current drive capability of 50 mA min per amp, and is able to drive unlimited capacitive loads. With a low power supply current of 15 mA max for both amplifiers, the AD826 is a true general purpose operational amplifier.

The AD826 is ideal for power sensitive applications such as video cameras and portable instrumentation. The AD826 can operate from a single +5 V supply, while still achieving 25 MHz of bandwidth. Furthermore the AD826 is fully specified from a single +5 V to  $\pm 15$  V power supplies.

The AD826 excels as an ADC/DAC buffer or active filter in data acquisition systems and achieves a settling time of 70 ns to 0.01%, with a low input offset voltage of 2 mV max. The AD826 is available in small 8-lead plastic mini-DIP and SO packages.

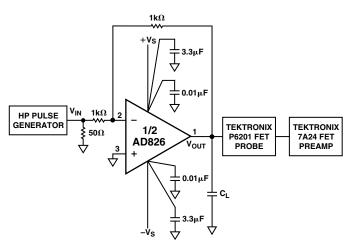

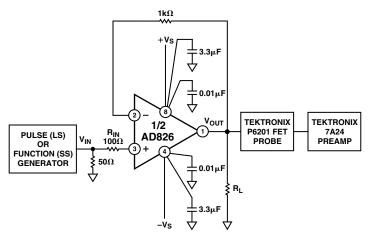

#### Driving a Large Capacitive Load

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

781/329-4700

www.analog.com

Fax:

781/461-3113

© Analog Devices, Inc., 2010

# **AD826—SPECIFICATIONS** (@ $T_A = +25^{\circ}C$ , unless otherwise noted)

| Parameter                         | Conditions                                                                                                                                                         | Vs                      | Min  | Тур   | Max   | Unit           |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------|-------|----------------|

| DYNAMIC PERFORMANCE               |                                                                                                                                                                    |                         |      |       |       |                |

| Unity Gain Bandwidth              |                                                                                                                                                                    | ±5 V                    | 30   | 35    |       | MHz            |

| 2                                 |                                                                                                                                                                    | ±15 V                   | 45   | 50    |       | MHz            |

|                                   |                                                                                                                                                                    | 0, +5 V                 | 25   | 29    |       | MHz            |

| Bandwidth for 0.1 dB Flatness     | Gain = +1                                                                                                                                                          | ±5 V                    | 10   | 20    |       | MHz            |

| Dandwidth for 0.1 dD 1 latitess   | Gam – T                                                                                                                                                            | ±15 V                   | 25   | 55    |       | MHz            |

|                                   |                                                                                                                                                                    | 0, +5 V                 | 10   | 20    |       | MHz            |

| Full Power Bandwidth <sup>1</sup> | $V_{OUT} = 5 V p-p$                                                                                                                                                | 0, 15 V                 | 10   | 20    |       |                |

| T un T öwer Dandwidth             | $R_{LOAD} = 500 \Omega$                                                                                                                                            | ±5 V                    |      | 15.9  |       | MHz            |

|                                   | $V_{OUT} = 20 \text{ V p-p}$                                                                                                                                       | ± 5 V                   |      | 15.9  |       |                |

|                                   |                                                                                                                                                                    | ±15 V                   |      | 5.6   |       | MHz            |

| Slam Data                         | $R_{LOAD} = 1 k\Omega$                                                                                                                                             |                         | 200  |       |       |                |

| Slew Rate                         | $R_{LOAD} = 1 k\Omega$                                                                                                                                             | ±5 V                    | 200  | 250   |       | V/µs           |

|                                   | Gain = -1                                                                                                                                                          | ±15 V                   | 300  | 350   |       | V/µs           |

|                                   |                                                                                                                                                                    | 0, +5 V                 | 150  | 200   |       | V/µs           |

| Settling Time to 0.1%             | –2.5 V to +2.5 V                                                                                                                                                   | ±5 V                    |      | 45    |       | ns             |

|                                   | $0 \text{ V}-10 \text{ V} \text{ Step}, A_{\text{V}} = -1$                                                                                                         | ±15 V                   |      | 45    |       | ns             |

| to 0.01%                          | -2.5 V to +2.5 V                                                                                                                                                   | ±5 V                    |      | 70    |       | ns             |

|                                   | $0 \text{ V}-10 \text{ V} \text{ Step}, \text{A}_{\text{V}} = -1$                                                                                                  | ±15 V                   |      | 70    |       | ns             |

| NOISE/ILADWONIO DEDEODUANOS       | L > V                                                                                                                                                              |                         |      |       |       | +              |

| NOISE/HARMONIC PERFORMANCE        |                                                                                                                                                                    |                         |      | -     |       | 110            |

| Total Harmonic Distortion         | $F_{\rm C} = 1 \text{ MHz}$                                                                                                                                        | ±15 V                   |      | -78   |       | dB             |

| Input Voltage Noise               | f = 10  kHz                                                                                                                                                        | ±5 V, ±15 V             |      | 15    |       | $nV/\sqrt{Hz}$ |

| Input Current Noise               | f = 10  kHz                                                                                                                                                        | ±5 V, ±15 V             |      | 1.5   |       | pA/√Hz         |

| Differential Gain Error           | NTSC                                                                                                                                                               | ±15 V                   |      | 0.07  | 0.1   | %              |

| $(R1 = 150 \ \Omega)$             | Gain = +2                                                                                                                                                          | ±5 V                    |      | 0.12  | 0.15  | %              |

| (111 130 1)                       |                                                                                                                                                                    | 0, +5 V                 |      | 0.15  | 0.115 | %              |

| Differential Phase Error          | NTSC                                                                                                                                                               | ±15 V                   |      | 0.11  | 0.15  | Degrees        |

|                                   |                                                                                                                                                                    |                         |      |       |       |                |

| $(R1 = 150 \ \Omega)$             | Gain = +2                                                                                                                                                          | $\pm 5 V$               |      | 0.12  | 0.15  | Degrees        |

|                                   |                                                                                                                                                                    | 0, +5 V                 |      | 0.15  |       | Degrees        |

| DC PERFORMANCE                    |                                                                                                                                                                    |                         |      |       |       |                |

| Input Offset Voltage              |                                                                                                                                                                    | $\pm 5$ V to $\pm 15$ V |      | 0.5   | 2     | mV             |

|                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                               |                         |      |       | 3     | mV             |

| Offset Drift                      |                                                                                                                                                                    |                         |      | 10    |       | µV/°C          |

| Input Bias Current                |                                                                                                                                                                    | ±5 V, ±15 V             |      | 3.3   | 6.6   | μA             |

| input Dias Suitent                | T <sub>MIN</sub>                                                                                                                                                   |                         |      | 5.5   | 10    | μA             |

|                                   |                                                                                                                                                                    |                         |      |       | 4.4   | · ·            |

| Lunt Offert Comment               | T <sub>MAX</sub>                                                                                                                                                   |                         |      | 05    |       | μA             |

| Input Offset Current              |                                                                                                                                                                    | ±5 V, ±15 V             |      | 25    | 300   | nA             |

|                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                               |                         |      |       | 500   | nA             |

| Offset Current Drift              |                                                                                                                                                                    |                         |      | 0.3   |       | nA/°C          |

| Open-Loop Gain                    | $V_{OUT} = \pm 2.5 V$                                                                                                                                              | ±5 V                    |      |       |       |                |

|                                   | $R_{LOAD} = 500 \Omega$                                                                                                                                            |                         | 2    | 4     |       | V/mV           |

|                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                               |                         | 1.5  |       |       | V/mV           |

|                                   | $R_{LOAD} = 150 \Omega$                                                                                                                                            |                         | 1.5  | 3     |       | V/mV           |

|                                   | $V_{OUT} = \pm 10 \text{ V}$                                                                                                                                       | ±15 V                   |      |       |       |                |

|                                   | $R_{LOAD} = 1 k\Omega$                                                                                                                                             |                         | 3.5  | 6     |       | V/mV           |

|                                   | $T_{MIN}$ to $T_{MAX}$                                                                                                                                             |                         | 2    | 5     |       | V/mV           |

|                                   | $V_{OUT} = \pm 7.5 V$                                                                                                                                              | ±15 V                   | 4    | ,     |       | V/III V        |

|                                   |                                                                                                                                                                    | V CI -                  | 2    | 4     |       | V/mV           |

|                                   | $R_{LOAD} = 150 \Omega (50 \text{ mA Output})$                                                                                                                     |                         | 2    | ч     |       | v/III V        |

| INPUT CHARACTERISTICS             |                                                                                                                                                                    |                         |      |       |       |                |

| Input Resistance                  |                                                                                                                                                                    |                         |      | 300   |       | kΩ             |

| Input Capacitance                 |                                                                                                                                                                    |                         |      | 1.5   |       | pF             |

| Input Common-Mode Voltage Range   |                                                                                                                                                                    | ±5 V                    | +3.8 | +4.3  |       | V              |

| 1                                 |                                                                                                                                                                    |                         | -2.7 | -3.4  |       | v              |

|                                   |                                                                                                                                                                    | ±15 V                   | +13  | +14.3 |       | v              |

|                                   |                                                                                                                                                                    | × • • •                 | -12  | -13.4 |       | V              |

|                                   |                                                                                                                                                                    | 0 +5 V                  |      |       |       | V              |

|                                   | 1                                                                                                                                                                  | 0, +5 V                 | +3.8 | +4.3  |       |                |

|                                   |                                                                                                                                                                    |                         |      |       |       | 37             |

|                                   |                                                                                                                                                                    |                         | +1.2 | +0.9  |       | V              |

| Common-Mode Rejection Ratio       | $V_{CM} = \pm 2.5 \text{ V},  \text{T}_{\text{MIN}} - \text{T}_{\text{MAX}}$                                                                                       | ±5 V                    | 80   | 100   |       | dB             |

| Common-Mode Rejection Ratio       | $V_{CM} = \pm 2.5 \text{ V},  \text{T}_{\text{MIN}} - \text{T}_{\text{MAX}}$ $V_{CM} = \pm 12 \text{ V}$ $\text{T}_{\text{MIN}} \text{ to } \text{T}_{\text{MAX}}$ | ±5 V<br>±15 V<br>±15 V  |      |       |       |                |

|                                    |                                                                        | <b>X</b> 7              | 15.   | т    |          | <b>T</b> T •/ |

|------------------------------------|------------------------------------------------------------------------|-------------------------|-------|------|----------|---------------|

| Parameter                          | Conditions                                                             | Vs                      | Min   | Тур  | Max      | Unit          |

| OUTPUT CHARACTERISTICS             |                                                                        |                         |       |      |          |               |

| Output Voltage Swing               | $R_{LOAD} = 500 \Omega$                                                | ±5 V                    | 3.3   | 3.8  |          | ±V            |

|                                    | $R_{LOAD} = 150 \Omega$                                                | ±5 V                    | 3.2   | 3.6  |          | ±V            |

|                                    | $R_{LOAD} = 1 k\Omega$                                                 | ±15 V                   | 13.3  | 13.7 |          | ±V            |

|                                    | $R_{LOAD} = 500 \Omega$                                                | ±15 V                   | 12.8  | 13.4 |          | ±V            |

|                                    | $R_{LOAD} = 500 \Omega$                                                | 0, +5 V                 | +1.5, |      |          |               |

|                                    |                                                                        |                         | +3.5  |      |          | V             |

| Output Current                     |                                                                        | ±15 V                   | 50    |      |          | mA            |

|                                    |                                                                        | ±5 V                    | 50    |      |          | mA            |

|                                    |                                                                        | 0, +5 V                 | 30    |      |          | mA            |

| Short-Circuit Current              |                                                                        | ±15 V                   |       | 90   |          | mA            |

| Output Resistance                  | Open Loop                                                              |                         |       | 8    |          | Ω             |

| MATCHING CHARACTERISTICS           |                                                                        |                         |       |      |          |               |

| Dynamic                            |                                                                        |                         |       |      |          |               |

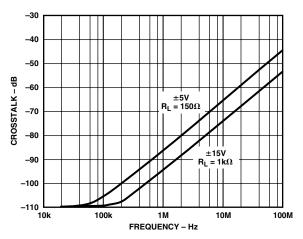

| Crosstalk                          | f = 5 MHz                                                              | ±15 V                   |       | -80  |          | dB            |

| Gain Flatness Match                | G = +1, f = 40 MHz                                                     | ±15 V                   |       | 0.2  |          | dB            |

| Slew Rate Match                    | G = -1                                                                 | ±15 V                   |       | 10   |          | V/µs          |

| DC                                 |                                                                        |                         |       |      |          |               |

| Input Offset Voltage Match         | $T_{MIN} - T_{MAX}$                                                    | $\pm 5$ V to $\pm 15$ V |       | 0.5  | 2        | mV            |

| Input Bias Current Match           | $T_{MIN}-T_{MAX}$                                                      | $\pm 5$ V to $\pm 15$ V |       | 0.06 | 0.8      | μA            |

| Open-Loop Gain Match               | $V_0 = \pm 10 \text{ V}, \text{ R}_{\text{LOAD}} = 1 \text{ k}\Omega,$ |                         |       |      |          |               |

|                                    | T <sub>MIN</sub> -T <sub>MAX</sub>                                     | ±15 V                   | 0.15  | 0.01 |          | mV/V          |

| Common-Mode Rejection Ratio Match  | $V_{CM} = \pm 12 \text{ V}, \text{T}_{MIN} - \text{T}_{MAX}$           | ±15 V                   | 80    | 100  |          | dB            |

| Power Supply Rejection Ratio Match | $\pm 5$ V to $\pm 15$ V, T <sub>MIN</sub> -T <sub>MAX</sub>            |                         | 80    | 100  |          | dB            |

| POWER SUPPLY                       |                                                                        |                         |       |      |          |               |

| Operating Range                    | Dual Supply                                                            |                         | ±2.5  |      | $\pm 18$ | V             |

|                                    | Single Supply                                                          |                         | +5    |      | +36      | V             |

| Quiescent Current/Amplifier        |                                                                        | ±5 V                    |       | 6.6  | 7.5      | mA            |

|                                    | $T_{MIN}$ to $T_{MAX}$                                                 | ±5 V                    |       |      | 7.5      | mA            |

|                                    |                                                                        | ±15 V                   |       |      | 7.5      | mA            |

|                                    | $T_{MIN}$ to $T_{MAX}$                                                 | ±15 V                   |       | 6.8  | 7.5      | mA            |

| Power Supply Rejection Ratio       | $V_{\rm S} = \pm 5$ V to $\pm 15$ V, $T_{\rm MIN}$ to $T_{\rm MAX}$    |                         | 75    | 86   |          | dB            |

#### NOTES

<sup>1</sup>Full power bandwidth = slew rate/2  $\pi$  V<sub>PEAK</sub>.

Specifications subject to change without notice.

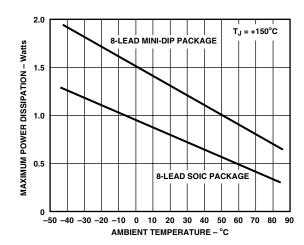

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage ±18 V                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>                                                                                                         |

| Plastic (N) See Derating Curves                                                                                                                 |

| Small Outline (R) See Derating Curves                                                                                                           |

| Input Voltage (Common Mode) $\dots \dots \dots$ |

| Differential Input Voltage ±6 V                                                                                                                 |

| Output Short Circuit Duration See Derating Curves                                                                                               |

| Storage Temperature Range (N, R) $\ldots \ldots -65^{\circ}C$ to $+125^{\circ}C$                                                                |

| Operating Temperature Range40°C to +85°C                                                                                                        |

| Lead Temperature Range (Soldering 10 seconds) +300°C                                                                                            |

|                                                                                                                                                 |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability .

<sup>2</sup>Specification is for device in free air: 8-lead plastic package,  $\theta_{JA} = 100^{\circ}$ C/watt; 8-lead SOIC package,  $\theta_{JA} = 155^{\circ}$ C/watt.

### ESD SUSCEPTIBILITY

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 volts, which readily accumulate on the human body and on test equipment, can discharge without detection. Although the AD826 features proprietary ESD protection circuitry, permanent damage may still occur on these devices if they are subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid any performance degradation or loss of functionality.

Maximum Power Dissipation vs. Temperature for Different Package Types

AD826 – Typical Characteristics

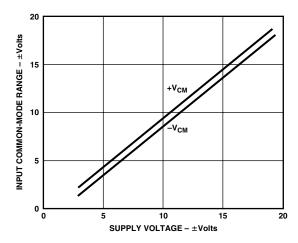

Figure 1. Common-Mode Voltage Range vs. Supply

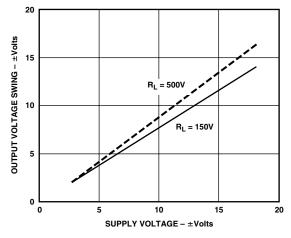

Figure 2. Output Voltage Swing vs. Supply

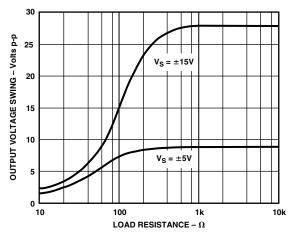

Figure 3. Output Voltage Swing vs. Load Resistance

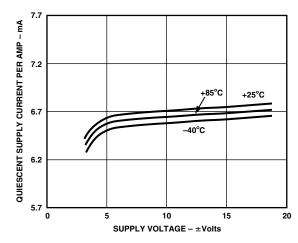

Figure 4. Quiescent Supply Current per Amp vs. Supply Voltage for Various Temperatures

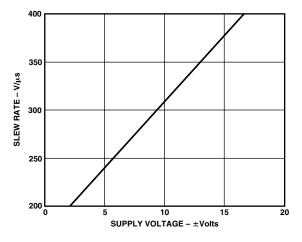

Figure 5. Slew Rate vs. Supply Voltage

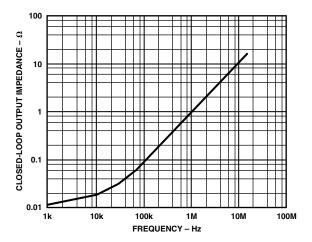

Figure 6. Closed-Loop Output Impedance vs. Frequency

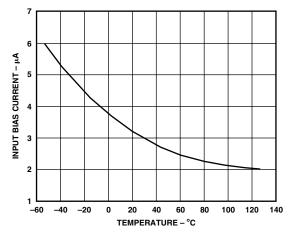

Figure 7. Input Bias Current vs. Temperature

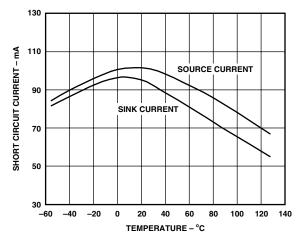

Figure 8. Short Circuit Current vs. Temperature

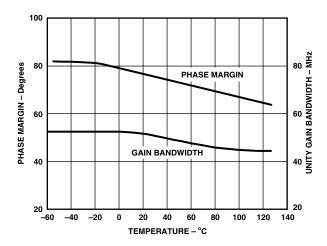

Figure 9. Unity Gain Bandwidth and Phase Margin vs. Temperature

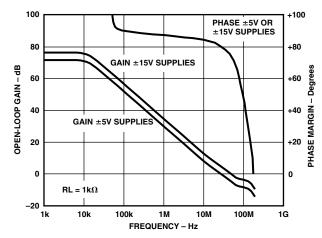

*Figure 10. Open-Loop Gain and Phase Margin vs. Frequency*

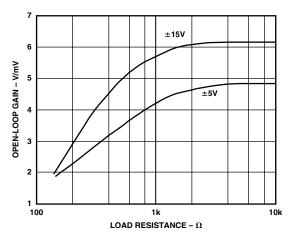

Figure 11. Open-Loop Gain vs. Load Resistance

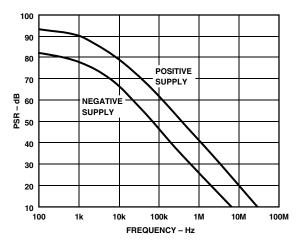

Figure 12. Power Supply Rejection vs. Frequency

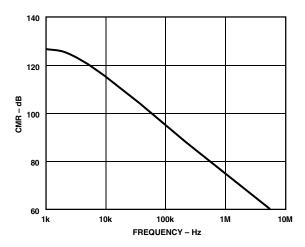

Figure 13. Common-Mode Rejection vs. Frequency

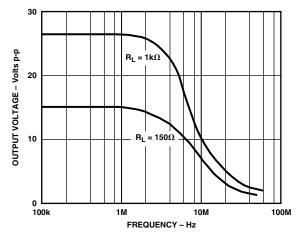

Figure 14. Large Signal Frequency Response

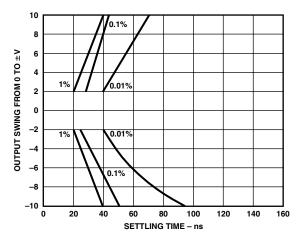

Figure 15. Output Swing and Error vs. Settling Time

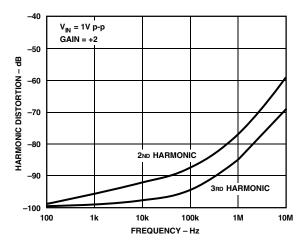

Figure 16. Harmonic Distortion vs. Frequency

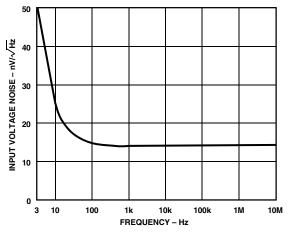

Figure 17. Input Voltage Noise Spectral Density

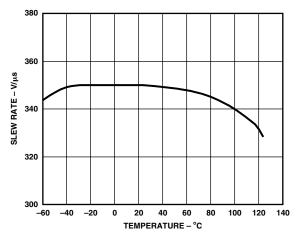

Figure 18. Slew Rate vs. Temperature

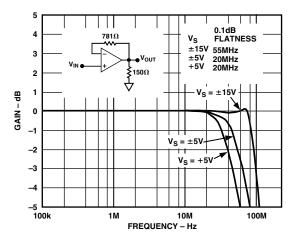

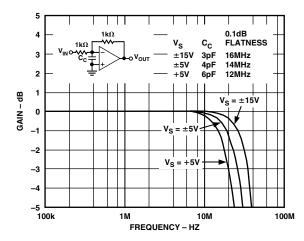

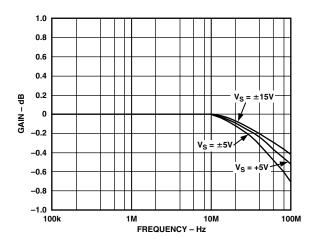

Figure 19. Closed-Loop Gain vs. Frequency

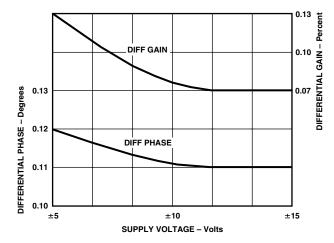

Figure 20. Differential Gain and Phase vs. Supply Voltage

Figure 21. Crosstalk vs. Frequency

Figure 22. Closed-Loop Gain vs. Frequency, Gain = -1

Figure 23. Gain Flatness Matching vs. Supply, G = +1

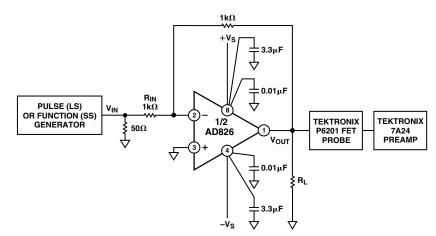

$\label{eq:RL} \begin{array}{l} \textbf{R}_L = 150\Omega \mbox{ FOR } \pm V_S = 5V, \mbox{ 1k}\Omega \mbox{ FOR } \pm V_S = 15V \\ \mbox{ USE GROUND PLANE} \\ \mbox{ PINOUT SHOWN IS FOR MINIDIP PACKAGE} \end{array}$

Figure 24. Crosstalk Test Circuit

Figure 25. Noninverting Amplifier Configuration

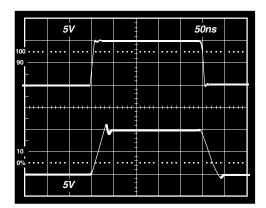

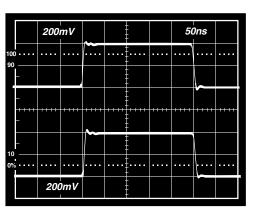

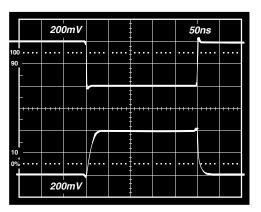

Figure 26. Noninverting Large Signal Pulse Response,  $R_L = 1 \ k\Omega$

Figure 27. Noninverting Large Signal Pulse Response,  $R_{\rm L}=150~\Omega$

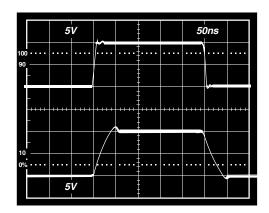

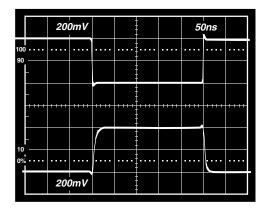

Figure 28. Noninverting Small Signal Pulse Response,  $R_L = 1 \ k\Omega$

Figure 29. Noninverting Small Signal Pulse Response,  $R_L = 150 \ \Omega$

Figure 30. Inverting Amplifier Configuration

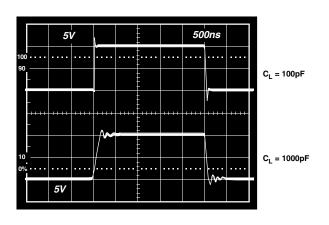

|                     | 5V    | /    |      |      |      |      | 50   | )ns      |      |

|---------------------|-------|------|------|------|------|------|------|----------|------|

| 100 • • • • •<br>90 | ••••• |      | •••• | •••• | •••• | •••• | •••• | ••••     |      |

|                     |       |      |      |      |      |      |      |          |      |

| -<br>               |       |      |      | ++++ |      |      |      |          |      |

| 10                  |       |      |      |      |      |      |      |          |      |

| 0%                  | ••••  | •••• | /    | •••• | •••• | •••• | •••• | <u>.</u> | •••• |

|                     | 5V    | /    |      |      |      |      |      |          |      |

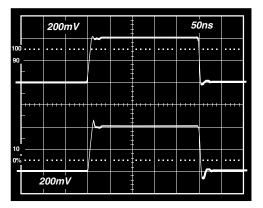

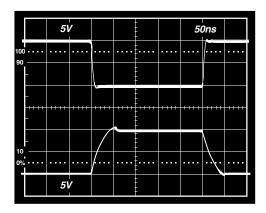

Figure 31. Inverting Large Signal Pulse Response,  $R_L = 1 \ k\Omega$

Figure 32. Inverting Large Signal Pulse Response,  $R_L = 150 \,\Omega$

Figure 33. Inverting Small Signal Pulse Response,  $R_{\rm L}=1~k\Omega$

Figure 34. Inverting Small Signal Pulse Response,  $R_L = 150 \,\Omega$

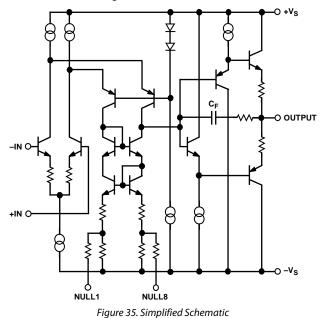

## THEORY OF OPERATION

The AD826 is a low cost, wide band, high performance dual operational amplifier which can drive heavy capacitive and resistive loads. It also achieves a constant slew rate, bandwidth and settling time over its entire specified temperature range.

The AD826 (Figure 35) consists of a degenerated NPN differential pair driving matched PNPs in a folded-cascode gain stage. The output buffer stage employs emitter followers in a class AB amplifier which delivers the necessary current to the load while maintaining low levels of distortion.

The capacitor,  $C_F$ , in the output stage mitigates the effect of capacitive loads. With low capacitive loads, the gain from the compensation node to the output is very close to unity. In this case,  $C_F$  is bootstrapped and does not contribute to the overall compensation capacitance of the device. As the capacitive load is increased, a pole is formed with the output impedance of the output stage. This reduces the gain, and therefore,  $C_F$  is incompletely bootstrapped. Effectively, some fraction of  $C_F$  contributes to the overall compensation capacitance, reducing the unity gain bandwidth. As the load capacitance is further increased, the bandwidth continues to fall, maintaining the stability of the amplifier.

## INPUT CONSIDERATIONS

An input protection resistor ( $R_{\rm IN}$  in Figure 25) is required in circuits where the input to the AD826 will be subjected to transient or continuous overload voltages exceeding the  $\pm 6$  V maximum differential limit. This resistor provides protection for the input transistors by limiting their maximum base current.

For high performance circuits, it is recommended that a "balancing" resistor be used to reduce the offset errors caused by bias current flowing through the input and feedback resistors. The balancing resistor equals the parallel combination of  $R_{\rm IN}$  and  $R_{\rm F}$  and thus provides a matched impedance at each input terminal. The offset voltage error will then be reduced by more than an order of magnitude.

## **APPLYING THE AD826**

The AD826 is a breakthrough dual amp that delivers precision and speed at low cost with low power consumption. The AD826 offers excellent static and dynamic matching characteristics, combined with the ability to drive heavy resistive and capacitive loads. As with all high frequency circuits, care should be taken to maintain overall device performance as well as their matching. The following items are presented as general design considerations.

## **Circuit Board Layout**

Input and output runs should be laid out so as to physically isolate them from remaining runs. In addition, the feedback resistor of each amplifier should be placed away from the feedback resistor of the other amplifier, since this greatly reduces inter-amp coupling.

## **Choosing Feedback and Gain Resistors**

In order to prevent the stray capacitance present at each amplifier's summing junction from limiting its performance, the feedback resistors should be  $\leq 1 \text{ k}\Omega$ . Since the summing junction capacitance may cause peaking, a small capacitor (1 pF–5pF) maybe paralleled with R<sub>F</sub> to neutralize this effect. Finally, sockets should be avoided, because of their tendency to increase interlead capacitance.

## **Power Supply Considerations**

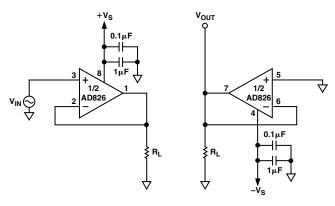

To ensure the proper operation of the AD826, connect the positive supply before the negative supply. Also, proper power supply decoupling is critical to preserve the integrity of high frequency signals. In carefully laid out designs, decoupling capacitors should be placed in close proximity to the supply pins, while their lead lengths should be kept to a minimum. These measures greatly reduce undesired inductive effects on the amplifier's response.

Though two 0.1  $\mu$ F capacitors will typically be effective in decoupling the supplies, several capacitors of different values can be paralleled to cover a wider frequency range.

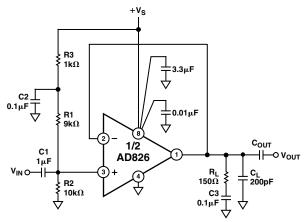

### **±SINGLE SUPPLY OPERATION**

An exciting feature of the AD826 is its ability to perform well in a single supply configuration (see Figure 37). The AD826 is ideally suited for applications that require low power dissipation and high output current and those which need to drive large capacitive loads, such as high speed buffering and instrumentation.

Referring to Figure 36, careful consideration should be given to the proper selection of component values. The choices for this particular circuit are: (R1 + R3) || R2 combine with C1 to form a low frequency corner of approximately 30 Hz.

Figure 36. Single Supply Amplifier Configuration

R3 and C2 reduce the effect of the power supply changes on the

output by low-pass filtering with a corner at  $\frac{1}{2\pi R_3 C_2}$ .

The values for  $R_L$  and  $C_L$  were chosen to demonstrate the AD826's exceptional output drive capability. In this configuration, the output is centered around 2.5 V. In order to eliminate the static dc current associated with this level, C3 was inserted in series with  $R_L$ .

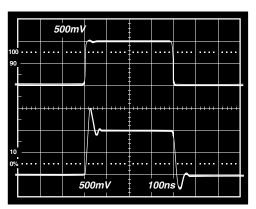

Figure 37. Single Supply Pulse Response, G = +1,  $R_L = 150 \Omega$ ,  $C_L = 200 pF$

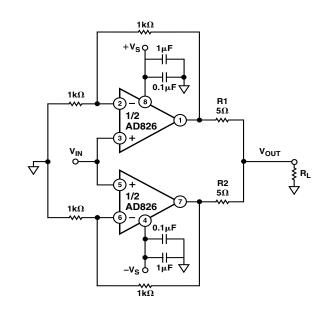

### PARALLEL AMPS PROVIDE 100 mA TO LOAD

By taking advantage of the superior matching characteristics of the AD826, enhanced performance can easily be achieved by employing the circuit in Figure 38. Here, two identical cells are paralleled to obtain even higher load driving capability than that of a single amplifier (100 mA min guaranteed). R1 and R2 are included to limit current flow between amplifier outputs that would arise in the presence of any residual mismatch.

Figure 38. Parallel Amp Configuration

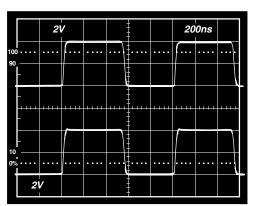

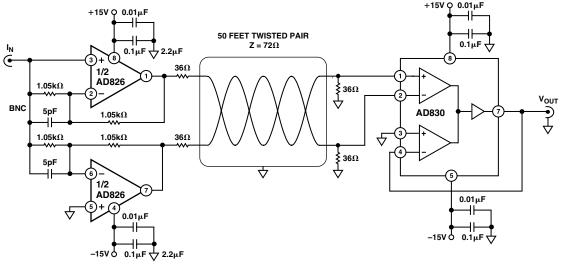

### SINGLE-ENDED TO DIFFERENTIAL LINE DRIVER

Outstanding CMRR (> 80 dB @ 5 MHz), high bandwidth, wide supply voltage range, and the ability to drive heavy loads, make the AD826 an ideal choice for many line driving applications. In this application, the AD830 high speed video difference amp serves as the differential line receiver on the end of a back terminated, 50 ft., twisted-pair transmission line (see Figure 40). The overall system is configured in a gain of +1 and has a -3 dB bandwidth of 14 MHz. Figure 39 is the pulse response with a 2 V p-p, 1 MHz signal input.

Figure 39. Pulse Response

Figure 40. Differential Line Driver

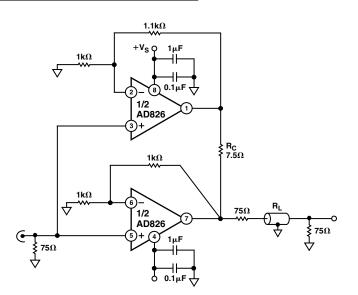

### LOW DISTORTION LINE DRIVER

The AD826 can quickly be turned into a powerful, low distortion line driver (see Figure 41). In this arrangement the AD826 can comfortably drive a 75  $\Omega$  back-terminated cable, with a 5 MHz, 2 V p-p input; all of this while achieving the harmonic distortion performance outlined in the following table.

| Configuration                                       | 2nd Harmonic |

|-----------------------------------------------------|--------------|

| 1. No Load                                          | -78.5 dBm    |

| $2. 150 \Omega R_L Only$                            | -63.8 dBm    |

| $\overline{3.\ 150\ \Omega\ R_L\ 7.5\ \Omega\ R_C}$ | -70.4 dBm    |

In this application one half of the AD826 operates at a gain of 2.1 and supplies the current to the load, while the other provides the overall system gain of 2. This is important for two reasons: the first is to keep the bandwidth of both amplifiers the same, and the second is to preserve the AD826's ability to operate from low supply voltages.  $R_C$  varies with the load and must be chosen to satisfy the following equation:

### $R_C = MR_L$

where *M* is defined by  $[(M+1) G_S = G_D]$  and  $G_D = Driver's$  Gain,  $G_S = System$  Gain.

Figure 41. Low Distortion Amplifier

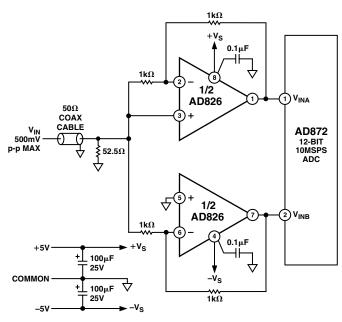

#### HIGH PERFORMANCE ADC BUFFER

Figure 42 is a schematic of a 12-bit high speed analog-to-digital converter. The AD826 dual op amp takes a single ended input and drives the AD872 A/D converter differentially, thus reducing 2nd harmonic distortion. Figure 43 is a FFT of a 1 MHz input, sampled at 10 MHz with a THD of -78 dB. The AD826 can be used to amplify low level signals so that the entire range of the converter is used. The ability of the AD826 to perform on a  $\pm 5$  volt supply or even with a single 5 volts combined with its rapid settling time and ability to deliver high current to complicated loads make it a very good flash A/D converter buffer as well as a very useful general purpose building block.

Figure 42. A Differential Input Buffer for High Bandwidth ADCs

| Vertical Scale<br>10.00 dB/dv<br>1   | Offset<br>-0.00 dB            | Marker Ampl<br>0.00 dB           | Marker Freg<br>986328.1 Hz |

|--------------------------------------|-------------------------------|----------------------------------|----------------------------|

| ·····                                |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               |                                  |                            |

|                                      |                               | 3                                |                            |

|                                      |                               | 7.1.1                            | 4<br>. 1.6 i               |

| han many history of the start of the | halandari kalandadari kalanda | angementer                       | Long Ann I di Arter Merud  |

|                                      |                               |                                  |                            |

| Horz Disp Line<br>Vert Disp Line     | Display Line 1                | Display Line 2                   | Delta                      |

| und Fra 986328<br>und BW 9766        |                               | 0.00 Harmo<br>8.17 2nd -83.8     | nics (dBc)                 |

| NR Strt 0<br>NR Stop 500000          | SNR 6                         | 3,85 3rd -81.9<br>3,69 4th -87.4 | 4 7th -90.8                |

| mpl Frq 1000000                      |                               | 1.94 5th -94.9                   |                            |

Figure 43. FFT, Buffered A/D Converter

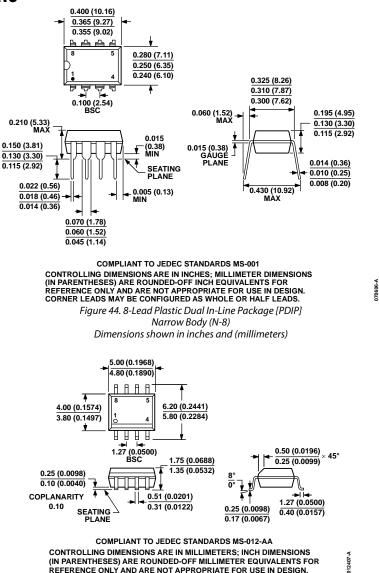

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012-AA CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. Figure 45. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| AD826AN            | -40°C to +85°C    | 8-Lead PDIP         | N-8            |

| AD826ANZ           | -40°C to +85°C    | 8-Lead PDIP         | N-8            |

| AD826AR            | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD826AR-REEL       | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD826AR-REEL7      | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD826ARZ           | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD826ARZ-REEL      | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| AD826ARZ-REEL7     | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

$^{1}$  Z = RoHS Compliant Part.

## **REVISION HISTORY**

| Changed Power Supply Bypassing Section to Power Supply |    |

|--------------------------------------------------------|----|

| Considerations Section                                 | 10 |

| Changes to Power Supply Considerations Section1        | .0 |

| Updated Outline Dimensions                             | 14 |

| Changes to Ordering Guide                              | 14 |

©2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D08950-0-4/10(C)

www.analog.com