02166766957 -02166766927

info@atrinelec.com

@atrinelec

**Triacs** logic level BT131 series

## **GENERAL DESCRIPTION**

Glass passivated, sensitive gate triacs in a plastic envelope, intended for use in general purpose bidirectional switching and phase control applications. These devices are intended to be interfaced directly to microcontrollers, logic integrated circuits and other low power gate trigger circuits.

## **QUICK REFERENCE DATA**

| SYMBOL                                                      | PARAMETER                                                                                                    | MAX.                         | MAX.                         | UNIT        |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------|

| V <sub>DRM</sub><br>I <sub>T(RMS)</sub><br>I <sub>TSM</sub> | BT131-<br>Repetitive peak off-state voltages<br>RMS on-state current<br>Non-repetitive peak on-state current | <b>500</b><br>500<br>1<br>16 | <b>600</b><br>600<br>1<br>16 | V<br>A<br>A |

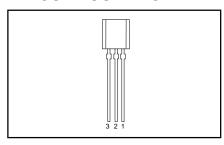

# **PINNING - TO92**

| PIN | DESCRIPTION     |  |  |

|-----|-----------------|--|--|

| 1   | main terminal 2 |  |  |

| 2   | gate            |  |  |

| 3   | main terminal 1 |  |  |

|     |                 |  |  |

# **PIN CONFIGURATION**

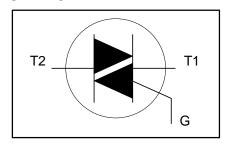

# **SYMBOL**

# **LIMITING VALUES**

Limiting values in accordance with the Absolute Maximum System (IEC 134).

| SYMBOL                                                                    | PARAMETER                                                                           | CONDITIONS MIN. MA                                                                                                                                                        |             | ۸X.                             | UNIT                            |                              |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------|---------------------------------|------------------------------|

| $V_{DRM}$                                                                 | Repetitive peak off-state voltages                                                  |                                                                                                                                                                           | -           | <b>-500</b><br>500 <sup>1</sup> | <b>-600</b><br>600 <sup>1</sup> | V                            |

| I <sub>T(RMS)</sub><br>I <sub>TSM</sub>                                   | RMS on-state current<br>Non-repetitive peak<br>on-state current                     | full sine wave; T <sub>lead</sub> ≤51 °C full sine wave; T <sub>j</sub> = 25 °C prior to surge t = 20 ms                                                                  | -<br>-      | 1                               |                                 | A                            |

| l²t<br>dl <sub>⊤</sub> /dt                                                | I <sup>2</sup> t for fusing<br>Repetitive rate of rise of<br>on-state current after | $ \begin{array}{l} t = 16.7 \text{ ms} \\ t = 10 \text{ ms} \\ I_{TM} = 1.5 \text{ A}; \ I_{G} = 0.2 \text{ A}; \\ dI_{G}/dt = 0.2 \text{ A}/\mu\text{s} \\ \end{array} $ | -<br>-      | 17<br>1.:                       | '.6<br>28                       | A<br>A <sup>2</sup> s        |

|                                                                           | triggering                                                                          | T2+ G+<br>T2+ G-<br>T2- G-<br>T2- G+                                                                                                                                      | -<br>-<br>- | 5<br>5                          | 0<br>0<br>0                     | A/μs<br>A/μs<br>A/μs<br>A/μs |

| $ \begin{vmatrix} I_{GM} \\ V_{GM} \\ P_{GM} \\ P_{G(AV)} \end{vmatrix} $ | Peak gate current Peak gate voltage Peak gate power Average gate power              | over any 20 ms period                                                                                                                                                     | -<br>-<br>- |                                 | 2<br>5<br>5<br>.5               | V<br>W<br>W                  |

| $\begin{bmatrix} T_{stg}^{G(AV)} \\ T_{j} \end{bmatrix}$                  | Storage temperature<br>Operating junction<br>temperature                            |                                                                                                                                                                           | -40<br>-    | 15                              | 50<br>25                        | °C                           |

April 1998 1 Rev 1.000

<sup>1</sup> Although not recommended, off-state voltages up to 800V may be applied without damage, but the triac may switch to the on-state. The rate of rise of current should not exceed 3 Å/µs.

Triacs logic level

BT131 series

# THERMAL RESISTANCES

| SYMBOL                 | PARAMETER                                                                  | CONDITIONS                                                | MIN. | TYP.          | MAX.          | UNIT              |

|------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|------|---------------|---------------|-------------------|

| R <sub>th j-lead</sub> | Thermal resistance junction to lead Thermal resistance junction to ambient | full cycle<br>half cycle<br>pcb mounted;lead length = 4mm |      | -<br>-<br>150 | 60<br>80<br>- | K/W<br>K/W<br>K/W |

# STATIC CHARACTERISTICS

T<sub>i</sub> = 25 °C unless otherwise stated

| SYMBOL                                                                               | PARAMETER                 | CONDITIONS                                                              | I    | MIN. | TYP. | MAX.        | UNIT |

|--------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------|------|------|------|-------------|------|

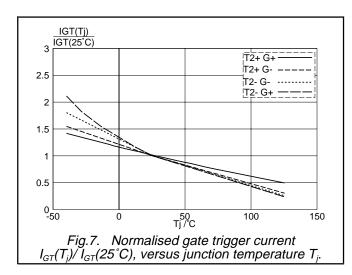

| I <sub>GT</sub>                                                                      | Gate trigger current      | $V_D = 12 \text{ V}; I_T = 0.1 \text{ A}$                               |      |      |      |             |      |

|                                                                                      |                           |                                                                         | + G+ | -    | 0.4  | 3           | mΑ   |

|                                                                                      |                           | T2+                                                                     | + G- | -    | 1.3  | 3<br>3      | mΑ   |

|                                                                                      |                           | T2-                                                                     | - G- | -    | 1.4  | 3           | mΑ   |

|                                                                                      |                           | T2-                                                                     | - G+ | -    | 3.8  | 7           | mΑ   |

| l <sub>L</sub>                                                                       | Latching current          | $V_D = 12 \text{ V}; I_{GT} = 0.1 \text{ A}$                            |      |      |      |             |      |

| -                                                                                    |                           | T2+                                                                     | + G+ | -    | 1.2  | 5           | mΑ   |

|                                                                                      |                           | T2+                                                                     | + G- | -    | 4.0  | 8           | mΑ   |

|                                                                                      |                           | T2-                                                                     | - G- | -    | 1.0  | 8<br>5<br>8 | mΑ   |

|                                                                                      |                           | T2-                                                                     | - G+ | -    | 2.5  | 8           | mΑ   |

| I <sub>H</sub>                                                                       | Holding current           | $V_D = 12 \text{ V}; I_{GT} = 0.1 \text{ A}$                            |      | -    | 1.3  | 5           | mΑ   |

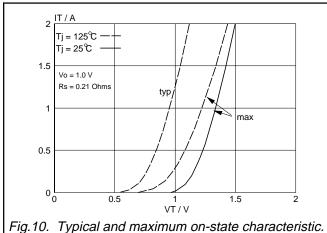

| $egin{array}{c} oldsymbol{I}_{H} \ oldsymbol{V}_{T} \ oldsymbol{V}_{GT} \end{array}$ | On-state voltage          | $I_{T} = 2.0 \text{ A}$                                                 |      | -    | 1.2  | 1.5         | V    |

| $V_{GT}$                                                                             | Gate trigger voltage      | $\dot{V}_{D} = 12 \text{ V}; I_{T} = 0.1 \text{ A}$                     |      | -    | 0.7  | 1.5         | V    |

|                                                                                      |                           | $ V_D = 400 \text{ V}; I_T = 0.1 \text{ A}; T_i = 125 ^{\circ}\text{C}$ |      | 0.2  | 0.3  | -           | V    |

| $I_{D}$                                                                              | Off-state leakage current | $V_D = V_{DRM(max)}$ ; $T_j = 125 °C$                                   |      | -    | 0.1  | 0.5         | mA   |

# **DYNAMIC CHARACTERISTICS**

$T_i = 25$  °C unless otherwise stated

| SYMBOL              | PARAMETER                                      | CONDITIONS                                                                                                                                                             | MIN. | TYP. | MAX. | UNIT |

|---------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| dV <sub>D</sub> /dt | Critical rate of rise of                       | $V_{DM} = 67\% V_{DRM(max)}; T_j = 125 \text{ °C};$                                                                                                                    | 5    | 15   | -    | V/μs |

| t <sub>gt</sub>     | off-state voltage Gate controlled turn-on time | exponential waveform, $R_{GK} = 1 \text{ k}\Omega$<br>$I_{TM} = 1.5 \text{ A}$ ; $V_D = V_{DRM(max)}$ ; $I_G = 0.1 \text{ A}$ ;<br>$dI_G/dt = 5 \text{ A}/\mu\text{s}$ | -    | 2    | -    | μs   |

Triacs logic level

BT131 series

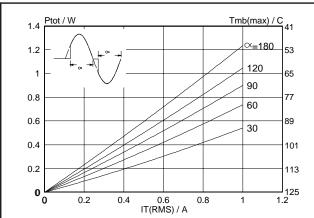

Fig.1. Maximum on-state dissipation,  $P_{tot}$ , versus rms on-state current,  $I_{T(RMS)}$ , where  $\alpha$  = conduction angle.

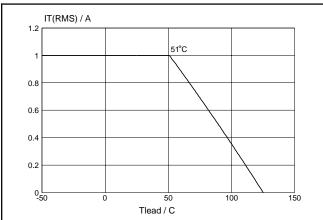

Fig.4. Maximum permissible rms current  $I_{T(RMS)}$ , versus lead temperature  $T_{lead}$ .

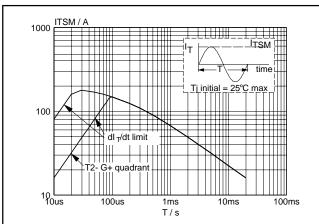

Fig.2. Maximum permissible non-repetitive peak on-state current  $I_{TSM}$ , versus pulse width  $t_p$ , for sinusoidal currents,  $t_p \le 20$ ms.

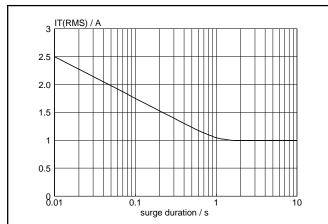

Fig.5. Maximum permissible repetitive rms on-state current  $I_{T(RMS)}$ , versus surge duration, for sinusoidal currents, f = 50 Hz;  $T_{lead} \le 51$  °C.

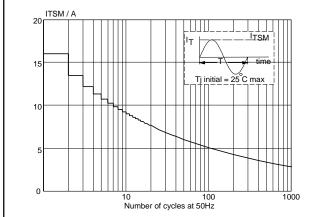

Fig.3. Maximum permissible non-repetitive peak on-state current  $I_{TSM}$ , versus number of cycles, for sinusoidal currents, f = 50 Hz.

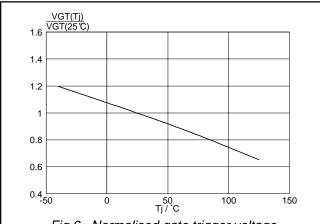

Fig.6. Normalised gate trigger voltage  $V_{GT}(T_j)/V_{GT}(25\,^{\circ}C)$ , versus junction temperature  $T_j$ .

Fig.10. Typical and maximum on-state characteristic.

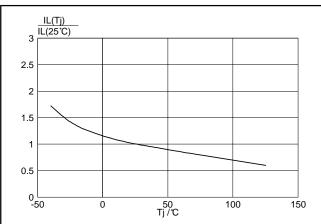

Fig.8. Normalised latching current  $I_L(T_j)/I_L(25^{\circ}C)$ , versus junction temperature  $T_j$ .

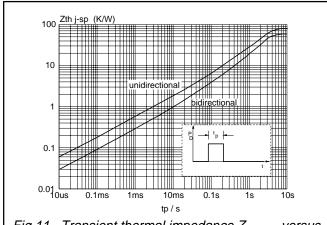

Fig.11. Transient thermal impedance  $Z_{th j-lead}$ , versus pulse width  $t_p$ .

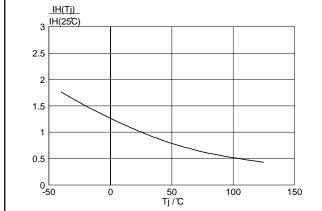

Fig.9. Normalised holding current  $I_H(T_i)/I_H(25^{\circ}C)$ , versus junction temperature  $T_j$ .

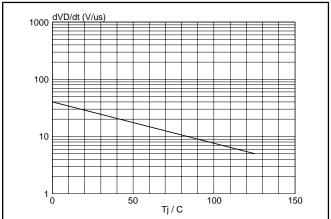

Fig.12. Typical, critical rate of rise of off-state voltage, dV<sub>D</sub>/dt versus junction temperature T<sub>j</sub>.

**Triacs** logic level BT131 series

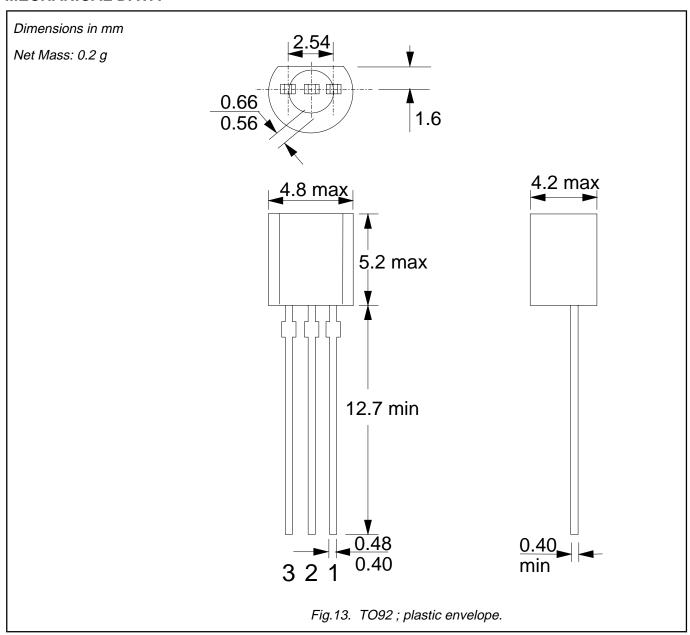

# **MECHANICAL DATA**

Notes

1. Epoxy meets UL94 V0 at 1/8".

Philips Semiconductors Product specification

Triacs logic level

BT131 series

## **DEFINITIONS**

| Data sheet status         |                                                                                       |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |

| Product specification     | This data sheet contains final product specifications.                                |  |  |  |  |

|                           |                                                                                       |  |  |  |  |

## Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

## **Application information**

Where application information is given, it is advisory and does not form part of the specification.

## © Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.